差分传输:LVPECL差分信号的输出比较

振荡器差分传输的输出比较

差分传输是一种信号传输技术,与传统的单端信号传输(使用一条信号线和一条接地线)不同。差分传输在两条导线上传输信号。这两个信号具有相同的幅度,但相位相反。在这两条线上传输的信号即为差分信号。

LVPECL: 低电压正极耦合逻辑

LVPECL是PECL的优化版本,使用3.3V正向供电,而不是5V。PECL和LVPECL是差分信号系统,主要用于高速和时锺分配电路。一个常见的误解是PECL设备与ECL设备略有不同。事实上,每个ECL设备也是一个PECL设备。

LVDS: 低电压差分信号

LVDS是一种电子信号系统,能够满足当今高性能数据传输须求。当系统电源电压降低到2V时,LVDS适用于比SVGA分辨率更高的TFT LCD显示设备。它已被广泛应用于各种设备中,可以嵌入FPGA、ASIC或其他组件中。

HCSL: 高速电流驱动逻辑

HCSL是一种基于电缆的、用于短距离串行高速数据传输的接口标准。它最独特的应用之一是PCI Express(PCIe)物理驱动器。这是HCSL驱动器阶段集成到芯片组中,用于连接个别的PCIe组件,例如将显卡连接到主机处理器。

差分信号与单端电路比较

相对于传统的单端信号传输中的信号线和地线,差分信号采用了不同的方法。

其优势包括:

- 强大的抗干扰能力。相位噪声通常同时应用于两条信号线,相位差为0。相位噪声对信号的逻辑意义没有影响。

- 有效抑制电磁干扰(EMI)。由于两根导线相距很近且信号幅度相等,两者之间及地线之间的耦合电磁场幅度也相等。信号的极性相反,电磁场将相互抵消。因此,对外部环境的电磁干扰也被最小化。

- 定时定位准确。差分信号的接收端是两条线上信号幅度差异正负变化的点。这被用作判断逻辑0/1过渡的点。普通的单端信号使用阈值电压作为信号逻辑0/1过渡点,受阈值电压与信号幅度电压比例影响很大,不适合低幅度信号。

输出比较

把各种输出水平、原理图和典型应用进行比较

Main Application, Output Level and Test Circuit

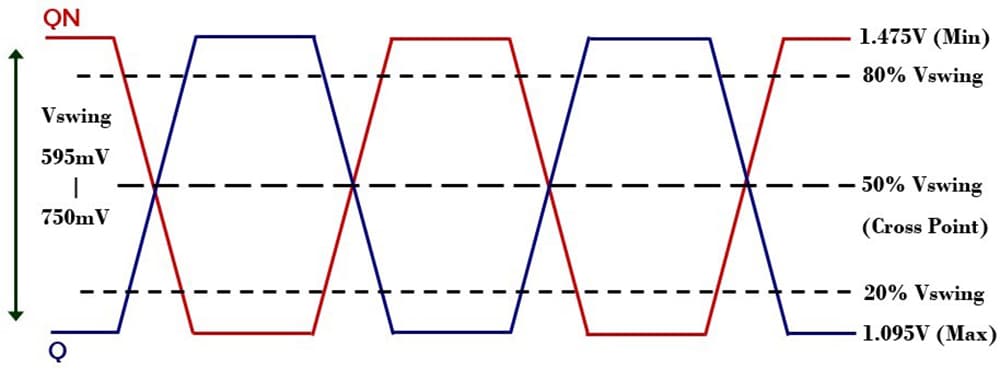

LVPECL Output Level

Vdd: 3.3V (1.68V~2.275V)

Vdd: 2.5V (1.095V ~ 1.475V)

LVDS Output Level

Vdd: 3.3V/2.5V/1.8V (0.9V ~ 1.6V) or wide voltage 1.63V ~ 3.63V (0.9V ~ 1.6V)

HCSL Output Leve

Vdd: 3.3V/2.5V/1.8V (-0.15V ~ 0.85V) or wide voltage 1.63V ~ 3.63V (-0.15V ~ 0.85V)

CMOS Output Level

Vdd: 5.0V (0.50V~4.50V)、3.3V (0.33V~2.97V)、2.5V (0.25V~2.25V)、1.8V (0.18V~1.62V) or wide voltage 1.62V ~ 3.63V (0.16V~3.63V)

注意:FPGA、以太网、摄象头、影象传感器、GPS 和人工智能等应用在设计中都高度须求 LVPECL、LVDS 和 HCSL。